CPLD - Complex Programmable Logic Devices CPLD - MAX V 440 Macro 74 IOs

画像は参考用です.

製品の詳細については、「製品仕様」を参照してください。

CPLD - Complex Programmable Logic Devices CPLD - MAX V 440 Macro 74 IOs

200 ドル以上のご注文には、限定版の中華風のギフトがプレゼントされます.

1000 ドルを超える注文は、30 ドルの配送料免除の対象となります.

5000 ドルを超える注文では、配送料と取引手数料が免除されます.

これらのオファーは新規顧客と既存顧客の両方に適用され、2024 年 1 月 1 日から 2024 年 12 月 31 日まで有効です。.

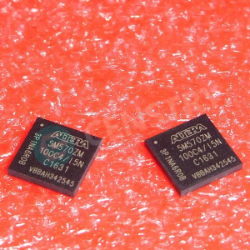

Altera

5M570ZM100I5N datasheet

MBGA100

ICチップ

Lead free/RoHS Compliant

Lead free/RoHS Compliant

今すぐ見積もりリクエストを送信してください。3 日以内に見積もりを提出する予定です。 7月 02, 2024。 今すぐご注文ください。以内に取引が完了する予定です。 7月 05, 2024。 追伸:時間はGMT+8:00に従います。

Altera

4000 PCS

EP4CE15E22C8N .PDF

Altera

1 PCS

EP3C16E144I7N .PDF

Altera

2000 PCS

EPM240T100I5N .PDF

Altera

2470 PCS

ES1030QI .PDF

2024-07-01

High quality suppliers.

2024-07-01

CENSTRY offers fast service, good pricing and good parts. Dale, Nick, Steve and Andrew are a true credit to our industry.

2024-06-30

Jen is wonderful and great to deal with

2024-06-29

Censtry is honest, reliable and professional.Great doing business with you. Thank you!

2024-06-27

Maryann Chuang is a nice lady!!! Good telephone phone skills and good attitue.

2024-06-23

Censtry Electronics is a wonderful customer! Jim is the best, very prefessional with fast shipping, hope to work more in the future!

2024-06-15

One of the good companies in China to provide good quality, original parts. always pleasure dealing with mike...

2024-05-30

perfect Sales team with perfect support, thanks

2024-04-28

Professional and reliable company.

2024-02-24

Quick response and on time delivery !

皆様からのフィードバックを非常に重視しております。 最も誠実なレビューを共有してください。

*コメントを投稿する前にアカウントにログインしてください